실제 연구원이 설계할 때 필요한 정보, 여기저기 흩어져있는 정보들의 핵심만 모았습니다.

저는 LVDS를 활용하는 실무 엔지니어로써, 여러분이 진짜 필요로 할 정보만 모아놨습니다.

1. 정의 및 간략 소개

낮은 전압 차등신호(Low voltage differential signaling, LVDS, 저전압 차등 시그널링)는 차등 신호(송신기에서 서로 반대되는 극성의 두 전압을 전송), 수신기에서 이신호를 비교하는 시스템이다. 그리고 수신기 쪽에 달린 두 선로 사이에 로드와 병렬로 달려있는 저항(Termination Resistor, 터미네이션 저항)을 통해 전류가 소모된다. 저항은 케이블의 Characteristic Impedance (특성 임피던스)에 맞게 100~120옴 정도로 설계한다.

LVDS는 신호의 진폭이 작고 두 선로가 전자기적으로 커플링되어 있기 때문에, RE(Radiated Emission)에 강하고 잡음에 강하며, 전력 소모가 작다.

정의와 소개를 더 알고싶다면 위키백과를 참조하세요.

https://ko.wikipedia.org/wiki/%EB%82%AE%EC%9D%80_%EC%A0%84%EC%95%95_%EC%B0%A8%EB%B6%84_%EC%8B%A0%ED%98%B8

낮은 전압 차분 신호 - 위키백과, 우리 모두의 백과사전

LVDS낮은 전압 차분 신호Low-voltage differential signaling (LVDS)발명 년도1994년속도655 Mbit/s (최대 속도 1-3 Gbit/s 가능) 낮은 전압 차등신호(Low voltage differential signaling, LVDS, 저전압 차등 시그널링)는 저렴

ko.wikipedia.org

2. Application: 속도 및 전송거리

속도는 M-LVDS가 50~100Mbps 정도가 나오고, LVDS가 1 Gbps 이상이 나온다. 따라서 50 Mbps 보다 빠른 인터페이스나 저전력 인터페이스를 구성하고자 한다면 LVDS는 꽤 좋은 솔루션이 될 것이다.

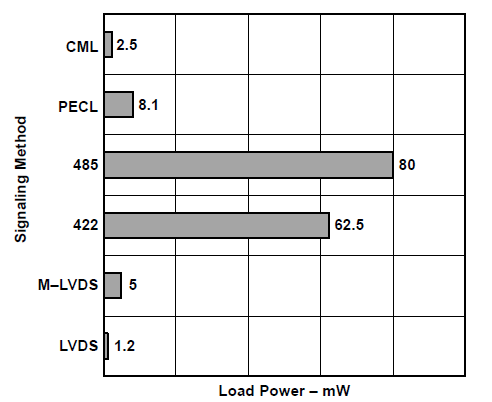

3. Differential Signal 들 간의 전력 비교

위 도표를 보면 LVDS가 저전력 Application에 얼마나 유리한지 알 수 있다. 원하는 속도(Signaling Rate)가 LVDS로 된다고 하면 LVDS를 선택하는 것이 상당이 유리할 수 있는 부분이다.

4. 차등 입력 전압의 임계값 (Differential Input Voltage Threshold)

설계시, 참고해야 하는 것이 아래의 임계값 표입니다. 왜냐하면 설계할 때 필연적으로 Failsafe Function을 넣게 되어있는데, 이때 저항값을 정할 때 임계값 전압을 계산해서 정해야하기 때문입니다.

Failsafe에 대하선 아래의 글을 참조하세요.

[살무] LVDS의 Fail-Safe 회로 이해 및 설계하기

(참고로 이런 것들은 TIA/EIA-644, TIA/EIA-899 등의 Standard를 따릅니다. 더 깊이 알고자 한다면 찾아보세요 ㅎㅎ)

최대 임계값과 최소 임계값 사이의 차동 입력 전압은 Transition 영역에 있으며, 결과적으로 불확정한 출력 상태가 됩니다. 출력이 High, Low 또는 상태 간 이동 중일 수 있습니다. 전환 중 출력의 시간 변동 동작은 수신기의 대역폭과 입력 전압의 시간 변동에 따라 달라집니다.

LVDS 라인 수신기를 약 100,000의 이득(Gain)이 있는 차동 증폭기로 간주합니다. VIT는 출력이 High와 Low 사이의 1/2이 되는 입력 전압이며, 히스테리시스에 대한 피드백이 없으면 출력이 High 또는 Low 상태로 전환되는 데 10초 이상의 uVolt만 필요합니다. 시스템에서 이 정도의 차동 노이즈가 발생할 가능성이 높으며, 임계값에 가까울 경우 출력의 진동이 발생할 수 있습니다.

- TI

5. 추천제품

| 제조사 | 파트명 | 설명 |

| THine | THC63LVDM87 / THC63LVD827 | 1.8V 동작의 저전압화를 실현하는 동시에, 출력 공통 모드 전압(Voc)을 수신측의Deserializer에 최적인 1.2V를 유지 |

| TI | SN65LVDS125DBT | 4채널, Signalling Rate가 1500Mbps로 고속에 속함 |

6. Reference:

- https://www.ti.com/lit/ds/symlink/sn65lvds32.pdf?HQS=dis-mous-null-mousermode-dsf-pf-null-wwe&ts=1649739472082&ref_url=https%253A%252F%252Fwww.mouser.kr%252F

- https://ko.wikipedia.org/wiki/%EB%82%AE%EC%9D%80_%EC%A0%84%EC%95%95_%EC%B0%A8%EB%B6%84_%EC%8B%A0%ED%98%B8

- https://www.thine.co.jp/ko/contents/detail/serdes-lvds.html

-----------------------------------------------------------------------------

다음 글: [Wiki] LVDS의 Fail-Safe 회로 이해 및 설계하기

[Wiki] LVDS의 Fail-Safe 회로 이해 및 설계하기

LVDS의 Fail-Safe 기능과 이를 구현하는 회로에 대해 알아보겠습니다. 일부는 번역을 활용했습니다. 그래도 이해하는데 문제 없도록 손봐놨으니, 이 글을 참조하시면 특히 실무자분들에게 도움이

johnnyjay.tistory.com

참고 글: [실무] RS-485 통신의 Failsafe 회로 이해+설계하기

[실무] RS-485 통신의 Failsafe 회로 이해+설계하기

안녕하세요! RS-485 통신은 거의 모든 산업분야에서 범용적으로 쓰이는 통신 방식중 하나이죠. Differential Voltage를 활용한 통신 방법으로, Data 전송에 있어서 안정성이 상당히 높아 장거리 통신도

johnnyjay.tistory.com

이 글을 PDF로 받기:

도움이 되었다면 즐겨찾기 추가, 공감 및 댓글 부탁드려요!

'전자 | 제어 | 항공우주 > 전자 HW 설계' 카테고리의 다른 글

| [실무] Push Pull Converter 설계 방법 - 기본 이론, 설계 (2) | 2022.05.04 |

|---|---|

| [기본&실무] LDO 레귤레이터 (ft.TI Datasheet) (0) | 2022.04.28 |

| [기초&실무] 슈미트 트리거(Schmitt Trigger) 및 디지털 회로 설계 (2) | 2022.04.18 |

| [실무] RS-485 통신의 Failsafe 회로 이해+설계하기 (0) | 2022.04.14 |

| [실무] LVDS의 Fail-Safe 회로 이해 및 설계하기 (0) | 2022.04.12 |

댓글