내가 아는 한, 대부분의 회로 설계자들은 LDO regulator 혹은 Switching Regulator를 사용하게 되어있다. 그 이유는 당연히 이 둘이 가격도 저렴하고 효율도 높기 때문이다. 그래서 이번 시간에는 LDO가 무엇인지 소개하면서 Datasheet를 이해하고 소자를 선택하기 위해 필요한 기본적인 용어와 정의를 소개할 것이다.

LDO 레귤레이터란?

LDO란?

Low Dropout Regulator (이하 LDO 레귤레이터 혹은 LDO)는 Low Dropout 단어 뜻 그대로 소자 내부에서 일어나는 전압강하가 아주 작아서 낮은 입출력 전위차로도 동작하는 선형 레귤레이터이다.

낮은 전압강하라는 말은, 사실상 전력 손실이 적어 발열이 그만큼 작다는 것을 의미한다.

디지털 회로들은 5V 혹은 3.3V를 가장 흔하게 쓰는데, 작은 회로 구성으로 5V를 3.3V로 만들어주기에는 LDO가 가장 적합하다.

1. Dropout Voltage

Dropout 전압은 간단히 말하면, LDO 레귤레이터가 Regulation에 필요한 전압이라고 이해해도 사실상 무방하다. 이를 좀 더 정확히 말하면 아래와 같다.

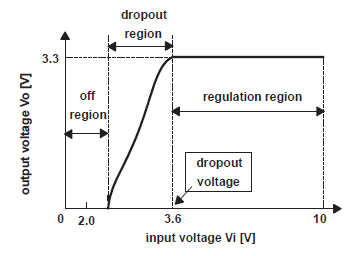

Dropout 전압은 회로가 입력 전압의 추가 감소에 대해 조절을 중단하는 입력 대 출력 차동 전압을 뜻한다. 이 지점은 입력 전압이 출력 전압에 근접할 때 발생한다. 그림 1은 일반적인 LDO 레귤레이터 회로를 나타낸다. Dropout 영역에서, PMOS 패스 요소는 단순히 저항이며 Dropout은 온저항(Ron)으로 표현된다.

V(dropout) = Io*Ron

예를 들어, 그림 2는 TPS76733 3.3-V LDO 레귤레이터의 입력/출력 특성을 보여준다. TPS76733의 Dropout 전압은 일반적으로 1A에서 350mV입니다. 따라서 LDO 레귤레이터는 3.65-V 입력 전압에서 빠지기 시작한다. Dropout 영역의 범위는 약 2-V와 3.65V 사이이다. 이 아래에서는 레귤레이터가 작동하지 않는다.

2. Quiescent Current (or Ground Current)

Quiescent Currernt 혹은 Ground Current는 입력 전류와 출력 전류의 차이를 뜻한다.

따라서 전류 효율을 극대화하려면 낮은 quiescent current가 필요하다. Iq = Ii - Io로 정의되며 이는 그림3과 같다.

(더 자세한 내용을 알고 싶다면 Reference 문서를 확인할 것을 추천한다)

3. Standby Current

Standby Current는 단어 뜻 그대로 대기 전류를 말한다. 출력이 제어신호(EN)에 의해 비활성화 되었을 때 레귤레이터가 대기중에 쓰는 전류를 말한다.

4. Efficiency

LDO 레귤레이터의 효율은 quiescent current와 입출력 전압에 의해 결정된다.

Efficiency = (Io*Vo) / ((Io+iq)*Vi) * 100%

높은 효율을 위해선, Dropout 전압과 quiescent current가 반드시 작아야한다. 또한, Power Dissipation이 LDO 레귤레이터의 효율 뜻하므로, 입출력 전압차가 최소화되어야 한다.

Power Dissipation = (Vi-Vo)*Io

5. Transient Response

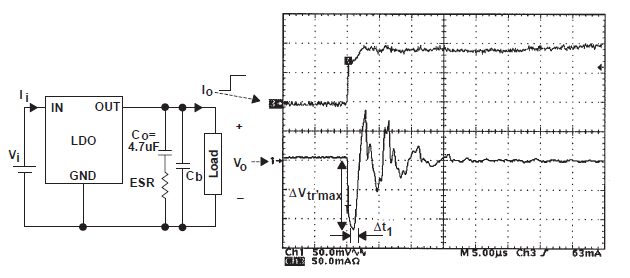

Transient Response는 한국어로는 보통 과도 응답 이라고 불리며, 로드의 전류 변화에 의해 허용되는 최대 출력 전압의 변동을 뜻한다.

과도응답은 출력 캐패시터 값(Co)과 출력 캐패시터의 등가직렬저항(ESR, Equivalent Series Resistance), 그리고 출력 캐패시터에 과도응답을 개선하기 위해 추가하는 바이패스 캐패시터(Cb), 그리고 최대 로드 전류(Io,max)에 의해 정해진다.

(이것도 공식이 있으나 LDO 반도체 설계자가 아니면 딱히 필요 없을 것 같아서 생략한다)

아래 그림5는 이해를 돕기위해 첨부하였다.

6. Line Regulation

Line Regulation은 입력전압이 출렁일 때, 출력전압을 유지하는 소자의 능력을 뜻한다.

Line Regulation = △Vo / △Vi

중요: 입력 공급 전압이 예민한 소자에는 Line Regulaion이 높은 LDO 소자를 사용하는 것이 바람직하다. ex) ADC

7. Load Regulation

Load Regulation은 로드가 변할 때 출력 전압을 유지하는 능력을 뜻한다.

Load Regulation = △Vo / △Io

(로드의 저항 값이 변하면 Io가 변할테니 Io로 계산한다)

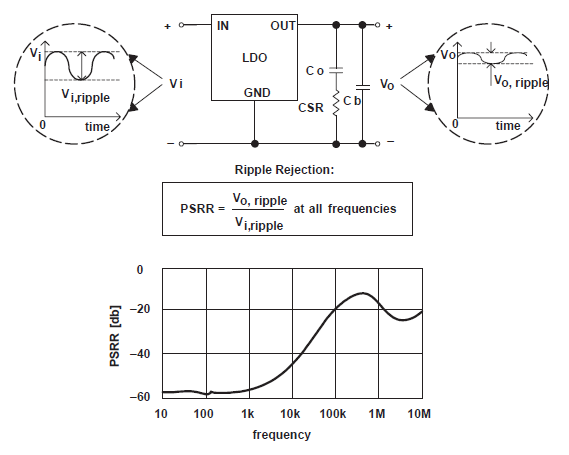

8. Power Supply Rejection

Power Supply Rejection Ratio (PSRR)은 Ripple Rejection이라고도 불리며, 입력 전압 변동으로 인한 출력 전압 변동을 방지하는 LDO 레귤레이터의 기능을 말한다. 전체 주파수 스펙트럼이 고려된다는 점을 제외하곤 line regulation과 동일한 관계가 PSRR에 적용된다.

중요: 입력전압에 Ripple이 있는데 이 노이즈가 회로에 영향을 미친다고 하면 PSRR을 고려하는 것이 바람직하다. 그렇지 않은 경우엔 딱히 볼 필요는 없다.

아래 그림을 보면 이해가 쉬울 것이다.

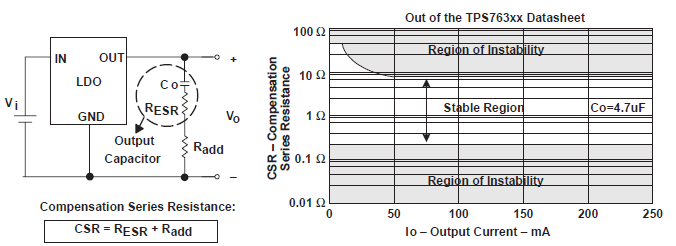

9. Instability of LDO Regulator

일반적으로 LDO 제조업체는 CSR(보상직렬저항) 값의 안정적인 범위를 보여주는 그래프를 제공한다. CSR은 출력 전류와 관련하여 불안정성을 유발할 수 있기 때문이다. CSR은 출력 캐패시턴스의 등가직렬저항(Resr)과 추가 저항(Radd)의 합을 나타낸다.

보통 하란대로 구성하면 딱히 문제되진 않는데, 확인은 필요하다.

마무리

이 정도 내용을 다 익히고 있다면 기초 이상은 하는 샘이다.

LDO 사용자로써 더 나아간다면, 회로의 전력계산이나 발열 계산을 위해 Power Dissipation과 Junction Temperature 등을 고려해야 하고,

LDO 설계자로써 더 나아간다면 고객이 요구하는 특성을 살리기 위해 PSRR과 출력저항 등의 관계를 더 공부해보면 될 것이다(매우 전문적인 영역임).

Reference

1. Texas Instrument - Understanding the Terms and Definitions of LDO Voltage

2. Rohm - LDO

3. Texas Instrument - TPS76733 Datasheet

이 글을 PDF로 받기:

도움이 되었다면 즐겨찾기 추가, 공감 및 댓글 부탁드려요!

'전자 | 제어 | 항공우주 > 전자 HW 설계' 카테고리의 다른 글

| [Embedded] [메모리 종류 - 1/3], 임베디드 시스템에서의 메모리 (1) | 2022.12.18 |

|---|---|

| [실무] Push Pull Converter 설계 방법 - 기본 이론, 설계 (2) | 2022.05.04 |

| [기초&실무] 슈미트 트리거(Schmitt Trigger) 및 디지털 회로 설계 (3) | 2022.04.18 |

| [실무] RS-485 통신의 Failsafe 회로 이해+설계하기 (2) | 2022.04.14 |

| [실무] LVDS의 Fail-Safe 회로 이해 및 설계하기 (1) | 2022.04.12 |

댓글