LVDS의 Fail-Safe 기능과 이를 구현하는 회로에 대해 알아보겠습니다.

일부는 번역을 활용했습니다. 그래도 이해하는데 문제없도록 손봐놨으니, 이 글을 참조하시면 특히 실무자분들에게 도움이 될 것이라 생각됩니다.

Fail-Safe Function (패일 세이프 기능)

대부분의 LVDS 수신기는 내부 또는 외부 Fail Safe 회로가 필요하므로 특정 연결 조건이나 문제 발생 시 수신기의 출력에 정해진 논리 조건이 필요합니다. 다음 목록에는 Fail-Safe 기능이 필요한 링크 조건 또는 문제 상황이 나와 있습니다.

- 개방 입력(Open Input): LVDS 칩에 여러 개의 수신기 포트가 있는 경우, 사용되지 않는 수신기 입력은 오픈 상태로 두어야 하며 출력은 안정적인 로직 하이여야 합니다.

- 플로트 입력(Float Input): LVDS 드라이버가 Tri-State에 있거나, 드라이버가 전원이 꺼지거나, 링크가 끊어진 경우 LVDS는 안정적인 로직 High 출력을 가져야 합니다.

- 단락 입력(Short Input): 두 개의 병렬 LVDS 와이어 또는 트레이스가 함께 단락된 경우, 이는 고장 연결이며 로직 High 출력 상태를 유지해야 합니다.

Fail Safe 기능이 노이즈가 많은 환경에서 견고하고 정상적인 LVDS 작동이 되어야 합니다.

Fail-Safe 회로 및 성능 분석

Fail-Safe 회로에는 기본적으로 외부 바이어스 회로, 내부 회로 및 병렬 회로의 세 가지 유형이 있습니다. 이러한 각 Fail-Safe 회로의 작동 방식을 설명한 다음 각각의 성능과 장단점을 분석하였습니다.

1. 외부 바이어싱 Fail-Safe 회로 (External-Biasing)

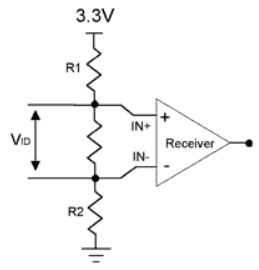

이 Fail-Safe 기능은 수신기 입력 핀에 외부로 연결된 3개의 저항기로 구성된 간단한 회로입니다.

이 설계에서 바이어싱은 라인이 구동되지 않을 때 두 입력 핀 사이에 양의 오프셋 전압을 설정하여 수신기의 출력이 로직 High 상태가 되도록 합니다. VID의 오프셋 값은 다음 식에 따라 설정됩니다.

그리고 공통모드 전압(Common-mode Voltage)는 다음의 식을 따릅니다.

이 Fail-Safe 회로는 초기 LVDS 수신기에 널리 사용되었다.

장점:

- 플로팅 라인(Floating Lin)의 노이즈 레벨에 따라 외부에서 오프셋 전압을 설정할 수 있는 유연성을 제공한다.

- ESD를 위한 공통 모드 복귀 경로 및 방전 경로를 제공한다.

단점:

- 두 개의 외부 저항기에 대한 요구 사항은 단일 LVDS 링크에 대한 부담이 될 수 있지만, 특히 다채널 애플리케이션에서 여러 개의 링크를 사용할 경우 문제가 될 수 있다.

- 오늘날 LVDS 데이터 전송 속도는 800Mbps 또는 컴퓨터 주변 장치 및 네트워크 상호 연결의 경우 2 Gbps 이상에 이를 수 있다. 이러한 고속 데이터 전송에서는 VID 오프셋에 의해 생성되는 불균형 수신기 임계값이 듀티 사이클에 상당한 왜곡을 일으키고 지터(신호의 진동)를 증가시킬 수 있다.

- VID 오프셋을 높게 설정할 수 없기 때문에 차동 노이즈의 경우 Fail-Safe에서 노이즈 마진이 낮다.

- 이 회로는 단락 입력 고장에 대해서는 작동하지 않는다. 레일이 단락되면 VID 오프셋 전압 소스도 단락 되고 LVDS 출력이 결정되지 않는다.

2. 경로 내 Fail-Safe 회로 (In-Path)

경로 내 Fail-Safe 설계는 외부 바이어싱 Fail-Safe 접근법과 유사하지만, 여기서 R1 및 R2는 LVDS 수신기에 통합되어 VID의 오프셋이 이제 내장 전압 소스가 된다는 점이 다릅니다. 이 회로는 일부 LVDS 수신기에서 광범위하게 사용되어 왔습니다. 아래 그림에는 이에 대한 Equivalant 회로가 나와 있습니다.

경로 내 회로 설계의 경우, VID의 내부 오프셋 값이 30mV에서 50mV 사이가 되도록 R1 및 R2 값이 선택합니다. 입력이 쇼트인 경우에도 양의 VID 오프셋이 삽입되므로 위의 세 가지 조건이 Fail-Safe 보호가 필요할 때마다 출력이 High 상태로 전환됩니다.

이 경로 내 설계는 외부 편향 방법을 넘어섰는데, 이는 외부 편향 방식의 단점 중 일부를 해결할 수 있습니다.

장점:

- 외부 저항이 필요 없다.

- 입력이 단락될 때도 작동한다.

단점:

- 오프셋 전압을 유연하게 설정할 수 없다.

- 이로 인해 수신기 임계값이 불균형하여 듀티 사이클이 저하되고 지터가 증가한다.

- '경로 내' 노이즈의 노이즈 마진이 낮다.

3. 병렬 Fail-Safe 회로 (Parallel)

병렬 Fail-Safe 회로는 다른 두 가지 Fail-Safe 회로의 주요 단점을 해결하며 아래 그림에 나와 있습니다.

그림과 같이 비교기는 레일의 전압 레벨을 모니터링하여 VCC - 0.3V의 기준과 비교합니다. 레일 전압 레벨이 기준보다 높으면 출력은 로직 High로 이동합니다. 그러면 이 논리 High 상태가 OR 게이트를 통해 수신기의 출력을 차단하고 Fail-Safe 기능이 활성화됩니다. 이 구성을 사용하면 앞에 나열된 Fail-Safe 기능(열림, 플로트 및 쇼트)이 필요한 세 가지 시나리오에서 LVDS 출력을 논리적으로 높게 끌어올 수 있습니다. 이 기능 설계는 공통 모드 전압이 기준 전압 VCC - 0.3V보다 작으면 제대로 작동할 수 있습니다.

병렬 Fail-Safe 방법은 두 가지 이전 방법에 비해 몇 가지 고유한 이점을 제공합니다.

- 공통 모드와 차동 모드 모두에서 훨씬 높은 노이즈 마진을 가지고 있다.

- 구성은 대칭적이며 입력 차동 신호의 듀티 사이클 및 지터 저하가 없다.

고유한 이점에도 불구하고, 이 병렬 방법을 사용하는 것에 대한 문제가 있습니다. 멀티포인트 또는 장거리 포인트 투 포인트 애플리케이션의 경우 공통 로딩 캐패시턴스가 상대적으로 클 수 있습니다. 고장이 발생하면 이 회로는 공통 모드 전압 레벨을 VCC - 0.3V로 충전하는 데 다소 시간이 걸립니다. 그러면 Fail-Safe 기능에 활성화 지연이 추가됩니다.

4. 마무리

외부 바이어싱, 경로 내 회로, 그리고 병렬 회로라는 세 가지 다른 Fail-Safe 회로의 설계, 작동, 강점과 단점에 대해 알아봤습니다. 여기서 LVDS 페일 세이프 기능에 대한 완벽한 솔루션은 없다는 것을 알 수 있었습니다. 그래도 병렬 회로 설계 방법이 다른 두 가지 방법보다 더 많은 상황에서 잘 작동할 수 있다는 것을 알 수 있었습니다.

Reference:

[1] Maxim Integrated - Understanding LVDS Fail-Safe Circuits

[2] IEEE Std 1596.3-1996 IEEE Standard for Low-Voltage Differential Signals (LVDS) for Scalable Coherent Interface (SCI) (PDF)

[3] Data sheets of DC36C200, DS90C032, and DS90LV018

[4] Maxim LVDS Line Drivers/Receivers

--------------------------------------------------------

이전 글: [Wiki] LVDS 란? (저전압 차등 시그널링, Low Voltage Differential Signaling)

[Wiki] LVDS 란? (저전압 차등 시그널링, Low Voltage Differential Signaling)

실제 연구원이 설계할때 필요한 정보, 여기저기 흩어져있는 정보들을 모았습니다. 또한 History 같이 쓸데없는 글은 모두 제외!! 저는 LVDS를 활용하는 실무 엔지니어로써, 여러분이 진짜 필요로 할

johnnyjay.tistory.com

참고 글: [실무] RS-485 통신의 Failsafe 회로 이해+설계하기

[실무] RS-485 통신의 Failsafe 회로 이해+설계하기

안녕하세요! RS-485 통신은 거의 모든 산업분야에서 범용적으로 쓰이는 통신 방식중 하나이죠. Differential Voltage를 활용한 통신 방법으로, Data 전송에 있어서 안정성이 상당히 높아 장거리 통신도

johnnyjay.tistory.com

이 글을 PDF로 받기:

도움이 되었다면 즐겨찾기 추가, 공감 및 댓글 부탁드려요!

'전자 | 제어 | 항공우주 > 전자 HW 설계' 카테고리의 다른 글

| [실무] Push Pull Converter 설계 방법 - 기본 이론, 설계 (2) | 2022.05.04 |

|---|---|

| [기본&실무] LDO 레귤레이터 (ft.TI Datasheet) (0) | 2022.04.28 |

| [기초&실무] 슈미트 트리거(Schmitt Trigger) 및 디지털 회로 설계 (3) | 2022.04.18 |

| [실무] RS-485 통신의 Failsafe 회로 이해+설계하기 (2) | 2022.04.14 |

| [실무] LVDS 란? (저전압 차등 시그널링, Low Voltage Differential Signaling) (0) | 2022.04.12 |

댓글