이 글을 PDF로 보기

Intro

이전 글에서는 Look-Up Table (LUT) 구성 요소에 대해 알아봤습니다. LUT는 FPGA 내부에서 가장 중요한 두 가지 구성 요소 중 하나이며, 다른 하나는 플립플롭입니다. 플립플롭의 종류는 여러 가지가 있지만(JK, T, D) 가장 많이 사용되는 것은 D 플립플롭입니다.

D 플립플롭 (레지스터)

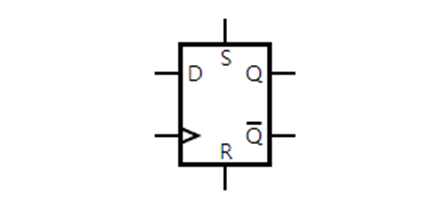

위 그림에서 장치의 상단에 S라는 레이블이 붙은 핀이 있습니다. 이 핀은 Set 핀으로 알려져 있습니다. 장치의 하단에는 R이라는 레이블이 붙은 핀이 있습니다. 이 핀은 Reset 핀으로 알려져 있습니다. 또한 장치의 오른쪽에는 Qbar라는 레이블이 붙은 핀이 있습니다. 이 핀은 항상 Q 핀의 값과 반대 값을 가집니다. 이제 이러한 핀들이 무엇인지 알았으니, 이 핀들은 지금 글에서는 신경쓰지 않을 것입니다. 플립플롭에서 가장 중요한 세 개의 핀은 다음과 같습니다:

- D: 플립플롭 Data Input

- Q: 플립플롭 Data Output (레지스터)

- >: 플립플롭의 Clock Input

여기서 여러분이 가장 먼저 궁금해할 질문은 "클록이란 무엇인가?"입니다.

Clock 이란

Digital Clock은 거의 모든 디지털 회로가 작동하도록 만드는 것입니다. System Clock을 기어 세트로 생각해보면 좋습니다. 시스템의 어떤 기어가 회전하려면 모든 다른 기어를 구동하는 마스터 기어가 있어야 합니다. 디지털 논리에서 클록의 역할이 바로 이런 것입니다. 클록은 FPGA가 원활하게 작동할 수 있도록 안정적인 흐름을 제공합니다.

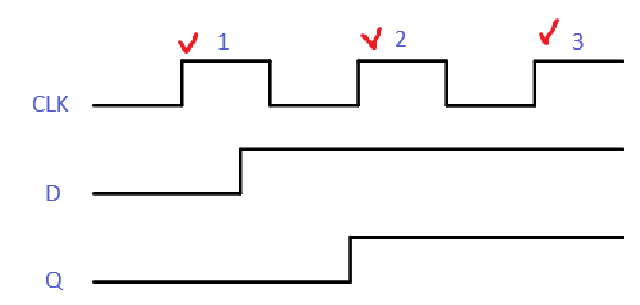

Clock은 플립플롭이 데이터 저장 요소로 사용될 수 있게 해줍니다. 모든 데이터 저장 요소는 순차 논리 또는 레지스터 논리로 알려져 있습니다. 순차 논리는 클록의 전환에 따라 작동합니다. 99.9%의 경우, 이는 상승 에지(클록이 0에서 1로 변할 때)입니다. 플립플롭은 클록의 상승 에지를 감지하면 입력 D의 데이터를 출력 Q로 등록합니다. 플립플롭은 복잡한 FPGA를 가능하게 만드는 요소입니다. 몇 가지 이벤트의 파형을 살펴보겠습니다.

D Flip-Flop

위의 파형은 세 개의 Clock cycle 이벤트를 보여줍니다. 빨간 체크표시는 클록의 상승 에지를 나타냅니다. 첫 번째와 두 번째 상승 에지 사이에서 D 입력이 Low에서 High로 변합니다. 출력 Q는 두 번째 클록 사이클의 상승 에지에서 D가 Low에서 High로 변했음을 감지합니다. 상승 에지는 플립플롭이 입력 데이터를 확인하는 시점입니다. 이 시점에서 Q는 입력 D와 같은 값을 갖게 됩니다. 세 번째 상승 에지에서 Q는 다시 D의 값을 확인하고 이를 등Register합니다(이것이 플립플롭이 종종 레지스터라고 불리는 이유입니다). D의 값이 변하지 않았으므로 Q는 계속 High 입니다. 또 다른 파형을 살펴보겠습니다.

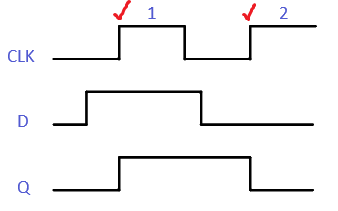

위 이미지는 D 플립플롭의 두 개의 입력과 하나의 출력을 보여주는 파형입니다. D 플립플롭은 클록의 Rising Edge에 민감하므로, Rising Edge 가 올 때 D 입력이 출력 Q로 전달됩니다. 이는 Edge에서만 발생합니다. 첫 번째 클록 사이클에서 Q는 D가 1로 변했음을 인식하여 0에서 1로 전환합니다. 두 번째 클록 에지에서 Q는 다시 D의 값을 확인하고 D가 다시 Low임을 확인하여 Low로 변합니다.

이제 플립플롭이 어떻게 작동하는지 이해했으니, 왜 디지털 설계에서 중요한지 알아보겠습니다. 다시 말하지만, 플립플롭과 LUT는 FPGA 내부에서 가장 중요한 두 가지 구성 요소입니다. 플립플롭(레지스터)의 작동 개념은 FPGA 프로그래머가 되는 데 필수적입니다. 이 작은 부품들은 어디에나 있습니다. 플립플롭은 FPGA에서 칩 내부 상태를 유지하는 데 사용되는 주요 구성 요소입니다.

모든 것이 LUT로만 구성된다면 FPGA에서 상태를 유지할 수 있는 방법이 없을 것입니다. 이는 FPGA가 이전에 무슨 일이 있었는지 알 수 없음을 의미합니다. 입력의 모든 변화는 즉시 평가되어 출력으로 전송되며, 매우 긴 AND 게이트, OR 게이트의 체인을 통해 이루어질 것입니다. 하지만 FPGA는 과거에 대한 정보를 알아야 대부분의 작업을 수행할 수 있습니다. 이를 통해 카운터, 상태 기계 및 사물의 상태를 추적할 수 있습니다. 플립플롭이 이를 가능하게 합니다. 이 개념이 아직 명확하지 않다면 괜찮습니다. 이는 추상적인 사고 방식입니다.

FPGA 설계에서 플립플롭의 중요성은 하드웨어 설명 언어(HDL)를 사용하여 작업할수록 더욱 분명해질 것입니다.

이제 디지털 설계의 기초를 배웠으니, HDL을 배우기 시작하면 됩니다.

그럼 화이팅!

'전자 | 제어 | 항공우주 > FPGA & HDL' 카테고리의 다른 글

| [FPGA 강의4] VHDL - 레지스터 기반 FIFO 설계 (2) | 2024.08.11 |

|---|---|

| [FPGA 강의3] FIFO 개념과 용도 (2) | 2024.08.11 |

| [FPGA 강의1] LUT (Look Up Table) (0) | 2024.08.10 |

| VS Code 에서 TerosHDL Linter를 GHDL로 사용하는 방법 (1) | 2024.04.07 |

| Verilig & VHDL 무료 프로그램 TOP 4 (3) | 2023.05.28 |

댓글